## Gate Interface Reliability in SiC/GaN **Power Devices**

Professor Layi Alatise and Dr Jose Ortiz Gonzalez 11<sup>th</sup> January 2021

WARWICK THE UNIVERSITY OF WARWICK

# **CONTENTS/OUTLINE** Silicon Carbide MOSFETs

Introduction

- WARWICK THE UNIVERSITY OF WARWICK

- Characterizing BTI using 3<sup>rd</sup> Quadrant Characteristics

- Characterizing BTI using Crosstalk

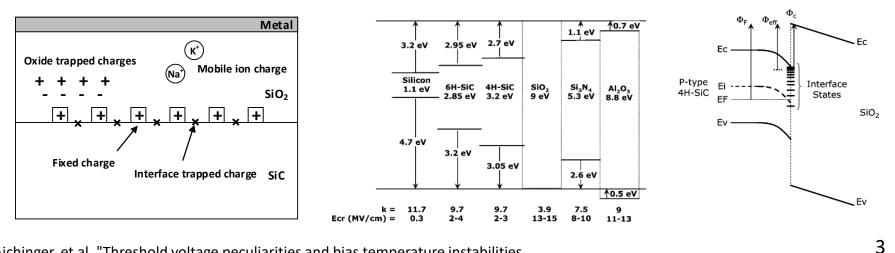

### INTRODUCTION TO OXIDE RELIABILITY

- Gate oxide has been/was a reliability concern in SiC MOSFETs

- Semiconductor-oxide interface

- SiC/SiO<sub>2</sub> is not Si/SiO<sub>2</sub> (more complex)

- Wider bandgap of SiC (3.3 eV) and narrower band offsets to the dielectric

- Existence of carbon

- Interface and near oxide trap density D<sub>it</sub> in SiC/SiO<sub>2</sub> is 100x D<sub>it</sub> in Si/SiO<sub>2</sub>

T. Aichinger, et al. "Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs," *Microelectronics Reliability,* vol. 80, pp. 68-78, 2018.

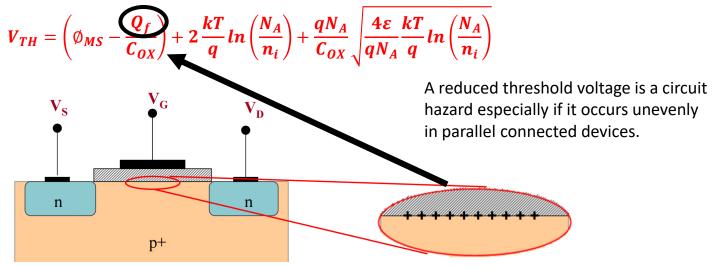

## INTRODUCTION TO OXIDE RELIABILITY

- The oxide interface between SiC and  $SiO_2$  is not as reliable as that between Si and VASiO<sub>2</sub>.

- Fixed oxide and interface traps capture electrons during positive bias and holes during negative bias. This causes a shift in V<sub>TH</sub> which is detrimental to device reliability.

Simplified MOSFET diagram showing MOS interface

### INTRODUCTION

Different studies had shown a reduced reliability of the gate oxide of SiC MOSFETs

#### • Just some examples. There are MANY more.

- R. Green, A. Lelis, and D. Habersat, "Threshold-voltage bias-temperature instability in commercially-available SiC MOSFETs," *Japanese Journal of Applied Physics*, vol. 55, no. 4S, p. 04EA03, 2016. (FREE ARTICLE)

- M. Beier-Moebius and J. Lutz, "Breakdown of Gate Oxide of SiC-MOSFETs and Si-IGBTs under High Temperature and High Gate Voltage," PCIM Conference, 2017

- T. Aichinger, G. Rescher, and G. Pobegen, "Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs," *Microelectronics Reliability*, vol. 80, pp. 68-78, 2018.

- K. Puschkarsky, H. Reisinger, T. Aichinger, W. Gustin, and T. Grasser, "Understanding BTI in SiC MOSFETs and its impact on circuit operation," *IEEE Trans. on Device and Materials Reliability*, vol. 18, no. 2, pp. 144 153, 2018.

- K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin, and H. Reisinger, "Review on SiC MOSFETs High-Voltage Device Reliability Focusing on Threshold Voltage Instability," *IEEE Trans. on Electron Devices*, vol. 66, no. 11, pp. 4604-4616, 2019.

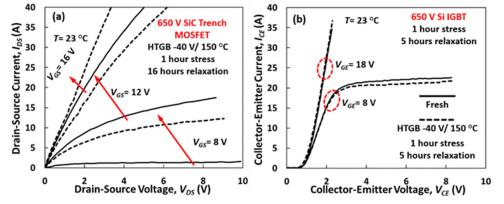

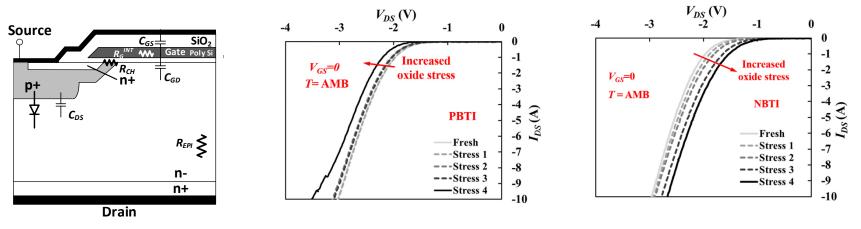

SiC and IGBT Gate Transfer characteristics before and after BTI Stressing

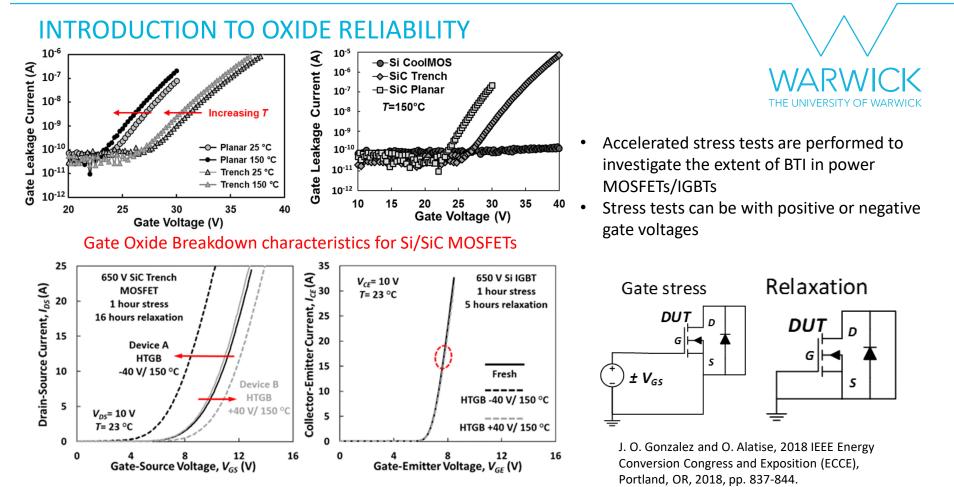

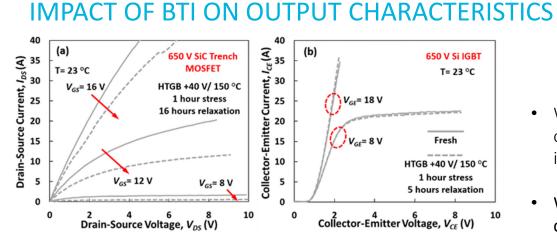

#### Impact of PBTI on the output characteristics of SiC and silicon IGBT

Impact of NBTI on the output characteristics of SiC MOSFET and silicon IGBT

- When a positive  $V_{\rm GS}$  stress is applied, negative charges are trapped in the oxide causing  $V_{\rm TH}$  increase. This is called PBTI.

- When a negative  $V_{\rm GS}$  stress is applied, positive charges are trapped in the oxide causing  $V_{\rm TH}$  decrease. This is called NBTI.

- The impact of  $V_{\rm TH}$  shift is to change the output and transfer characteristics of the device.

- The phenomenon occurs in silicon devices however, to a much reduced extent. In SiC, it is a more critical problem due to the lower quality oxide interface.

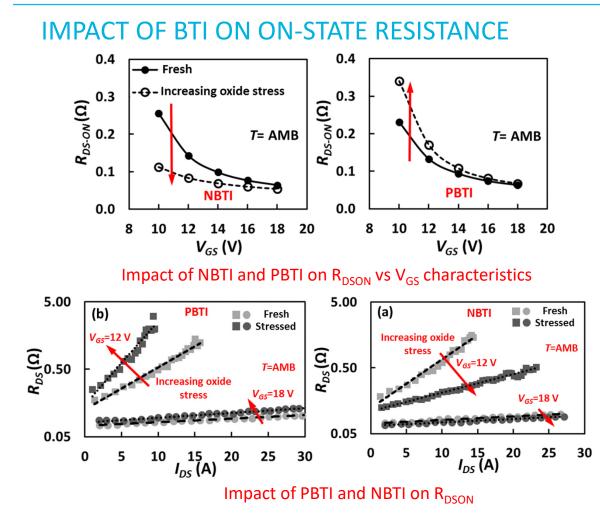

- For the SiC MOSFET, ON-state resistance increased under P-HTGB and reduced with N-HTGB

- This compromises R<sub>DSON</sub> as a TSEP

- It is more apparent at lower V<sub>GS</sub> because of the increased share of the channel resistance.

$$R_{DSON} = \frac{L_{ch}}{W\mu C_{OX}(V_{GS} - V_{TH})} + \frac{L_{drift}}{q\mu N_D A}$$

J. Ortiz Gonzalez and O. Alatise, "Bias temperature instability and condition monitoring in SiC power MOSFETs," *Microelectronics Reliability,* vol. 88-90, pp. 557-562, 2018.

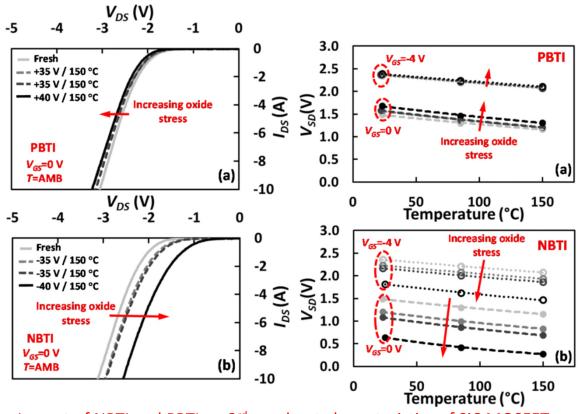

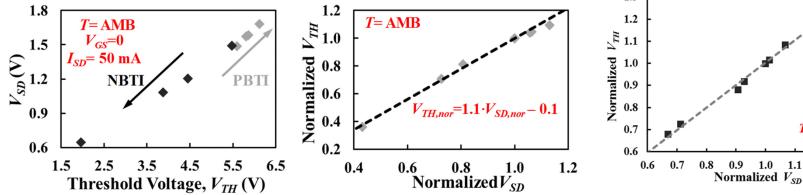

## IMPACT OF BTI ON 3<sup>RD</sup> QUADRANT CHARACTERISTICS

Impact of NBTI and PBTI on 3rd quadrant characteristics of SiC MOSFETs

- The change in V<sub>TH</sub> affects the 3<sup>rd</sup> quadrant (body diode) characteristics.

- 3<sup>rd</sup> quadrant characteristics are more affected by NBTI than PBTI.

- This is because increasing V<sub>TH</sub> reduces subthreshold conduction and hence, reduces the V<sub>SD</sub> dependence on V<sub>GS</sub>.

- The temperature sensitivity of V<sub>SD</sub> should account

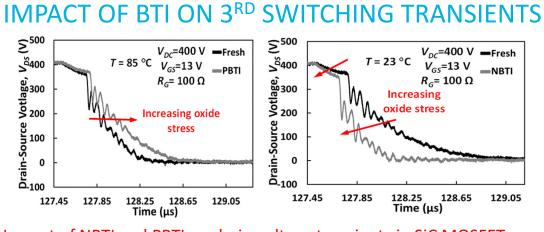

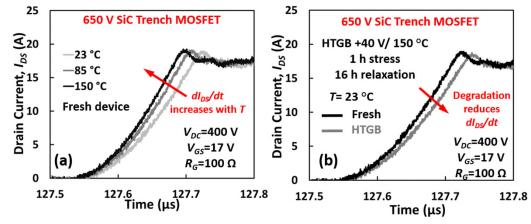

#### Impact of NBTI and PBTI on drain voltage transients in SiC MOSFETs

Impact of NBTI and PBTI on drain current transients in SiC MOSFETs

- The change in  $V_{TH}$  affects the turn-ON and turn-OFF  $V_{DS}$  and  $I_{DS}$  transients.

- PBTI causes delayed transients during turn-ON due to increase in  $V_{\text{TH}}.$

- NBTI causes accelerated transients during turn-ON due to reduction in V<sub>TH</sub>.

$$\frac{dI_{DS}}{dt} = \frac{\beta V_{GG}(V_{GS} - V_{TH})e^{-\frac{t}{R_G(C_{GS} + C_{GD})}}}{R_G(C_{GS} + C_{GD})}$$

$$\frac{dV_{DS}}{dt} = \frac{V_{GG} - V_{GP}}{R_G C_{GD}}$$

# **CONTENTS/OUTLINE** Silicon Carbide MOSFETs

WARWICK THE UNIVERSITY OF WARWICK

- Introduction

- Characterizing BTI using 3<sup>rd</sup> Quadrant Characteristics

- Characterizing BTI using Crosstalk

### CHARACTERIZING BIAS TEMPERATURE INSTABILITY

### • Some methods are proposed in:

- D. B. Habersat, A. J. Lelis, and R. Green, "Measurement considerations for evaluating BTI effects in SiC MOSFETs," Microelectronics Reliability, vol. 81, pp. 121-126, 2018

- G. Rescher, G. Pobegen, T. Aichinger, and T. Grasser, "Preconditioned BTI on 4H-SiC: Proposal for a Nearly Delay Time-Independent Measurement Technique," IEEE Trans. on Electron Devices, vol. 65, no. 4, pp. 1419-1426, 2018.

- K. Puschkarsky, H. Reisinger, T. Aichinger, W. Gustin, and T. Grasser, "Understanding BTI in SiC MOSFETs and its impact on circuit operation," IEEE Trans. on Device and Materials Reliability, vol. 18, no. 2, pp. 144 - 153, 2018.

- K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin, and H. Reisinger, "Review on SiC MOSFETs High-Voltage Device Reliability Focusing on Threshold Voltage Instability," IEEE Trans. on Electron Devices, vol. 66, no. 11, pp. 4604-4616, 2019.

### • Role of $V_{TH}$ shift in power cycling has also been evaluated

• H. Luo, F. Iannuzzo and M. Turnaturi, "Role of Threshold Voltage Shift in Highly Accelerated Power Cycling Tests for SiC MOSFET Modules," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 2, pp. 1657-1667, June 2020,

- Body diode voltage 3<sup>rd</sup> quadrant characteristics

- Current flowing through the channel due to partial turn-ON during reverse conduction when  $V_{GS}=0$

#### MOSFET with Body diode

#### Impact of NBTI and PBTI on 3<sup>RD</sup> Quadrant characteristics in SiC MOSFETs

J. A. O. González and O. Alatise, "A Novel Non-Intrusive Technique for BTI Characterization in SiC MOSFETs," in IEEE Transactions on Power Electronics, vol. 34, no. 6, pp. 5737-5747, June 2019,

J. Lutz et al., *Semiconductor Power Devices. Physics, Characteristics, Reliability*, 2nd ed.: Springer-Verlag Berlin Heidelberg, 2018

- Novel methodology for BTI characterization

- Using the body diode voltage when  $V_{GS}=0$

- Similar to the use of  $V_{SD}$  as temperature sensor, but for detecting oxide degradation/ $V_{TH}$ shifts.

- Calibration required. Using accelerated stress tests.

J. O. Gonzalez, O. Alatise and P. Mawby, "Non-Intrusive Methodologies for Characterization of Bias Temperature Instability in SiC Power MOSFETs," IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 2020, pp. 1-10

J. A. O. González and O. Alatise, "A Novel Non-Intrusive Technique for BTI Characterization in SiC MOSFETs," in IEEE Transactions on 14 Power Electronics, vol. 34, no. 6, pp. 5737-5747, June 2019,

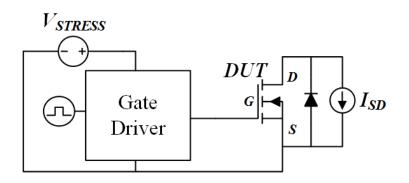

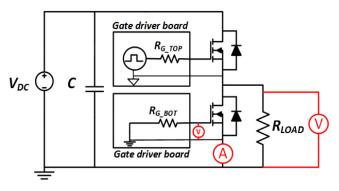

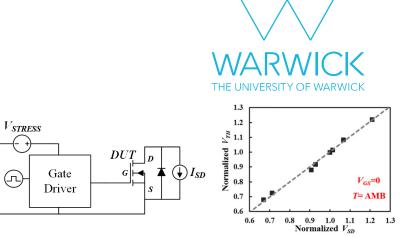

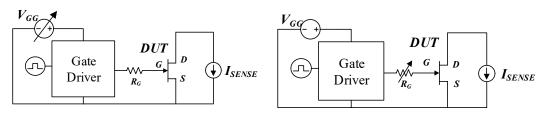

- Circuit

- Gate driver is used to apply stress voltage to the gate

- Constant current source: low sensing current I<sub>SD</sub> flowing in the source-drain direction

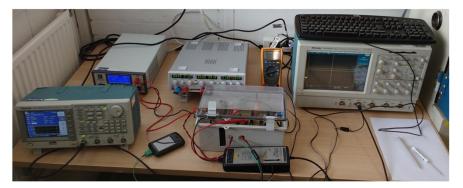

Experimental set-up for characterising BTI using 3<sup>rd</sup> quadrant characteristics

J. A. O. González and O. Alatise, "A Novel Non-Intrusive Technique for BTI Characterization in SiC MOSFETs," in IEEE Transactions on Power Electronics, vol. 34, no. 6, pp. 5737-5747, June 2019,

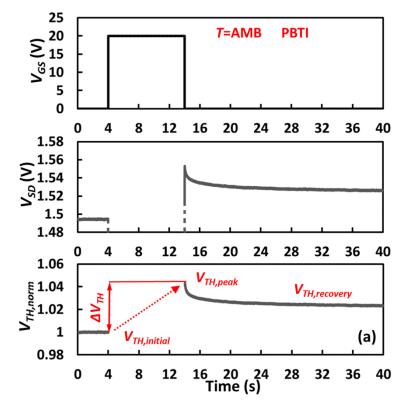

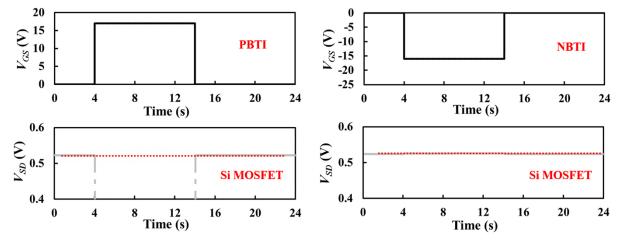

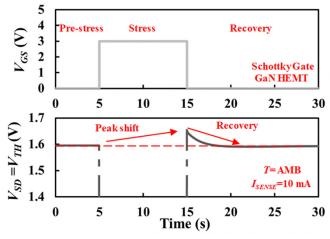

$V_{\text{GS}}, V_{\text{SD}}$  and  $V_{\text{TH}}$  during stress and recovery for PBTI

WARWICK THE UNIVERSITY OF WARWICK

- PBTI evaluation

- Pre-stress phase (V<sub>GS</sub>=0 V): The current flows through the body diode and channel. I<sub>SD</sub>= 50 mA , V<sub>TH,initial</sub>

- Stress phase (*V<sub>GS</sub>*=20 V): The current flows through channel. Device is ON.

- Recovery phase (V<sub>GS</sub>=0 V): The current flows through the body diode and channel. V<sub>TH,peak</sub> and V<sub>TH,recovery</sub>

J. Ortiz Gonzalez and O. Alatise, "Bias temperature instability and condition monitoring in SiC power MOSFETs," *Microelectronics Reliability*, vol. 88-90, pp. 557-562, 2018.

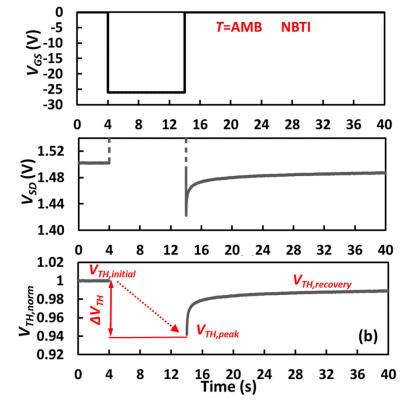

$V_{\text{GS}}\text{, }V_{\text{SD}}$  and  $V_{\text{TH}}$  during stress and recovery for NBTI

WARWICK THE UNIVERSITY OF WARWICK

- NBTI evaluation

- Pre-stress phase (V<sub>GS</sub>=0 V): The current flows through the body diode and channel. I<sub>SD</sub>= 50 mA , V<sub>TH,initial</sub>

- Stress phase (V<sub>GS</sub>=-26 V): The current flows through body diode only. SiC PN junction voltage

- Recovery phase (V<sub>GS</sub>=0 V): The current flows through the body diode and channel. V<sub>TH,peak</sub> and V<sub>TH,recovery</sub>

J. Ortiz Gonzalez and O. Alatise, "Bias temperature instability and condition monitoring in SiC power MOSFETs," *Microelectronics Reliability*, vol. 88-90, pp. 557-562, 2018.

Silicon MOSFET

#### • This is not observed for both positive and negative gate stresses

J. A. O. González and O. Alatise, "A Novel Non-Intrusive Technique for BTI Characterization in SiC MOSFETs," in IEEE Transactions on Power Electronics, vol. 34, no. 6, pp. 5737-5747, June 2019,

# **CONTENTS/OUTLINE** Silicon Carbide MOSFETs

- Introduction

- Characterizing BTI using 3<sup>rd</sup> Quadrant Characteristics

- Characterizing BTI using Crosstalk

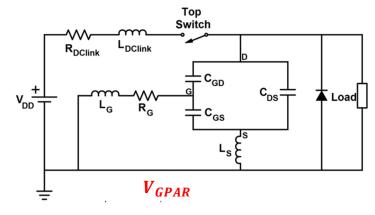

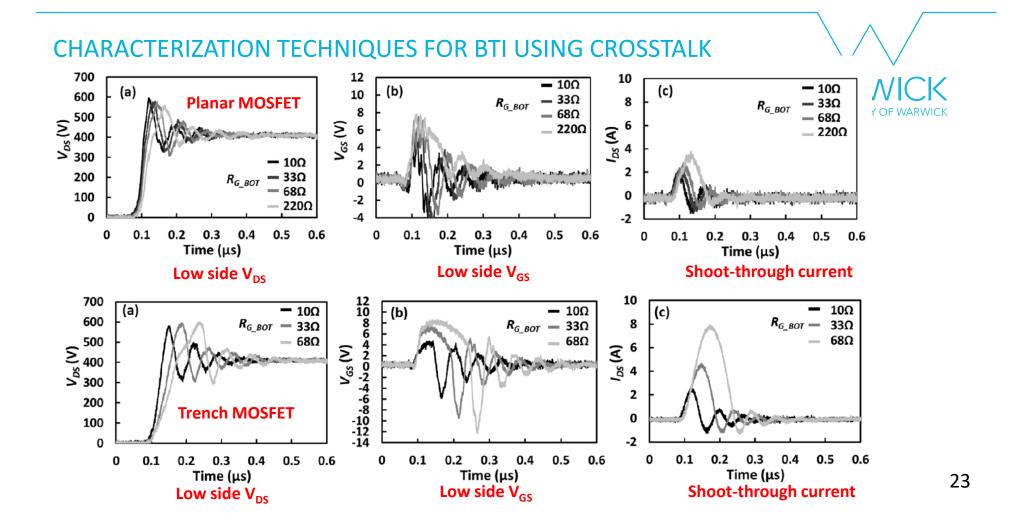

- As the top side device is switched ON, the supply voltage falls across the bottom side device with a dV/dt determined by the R<sub>GTOP</sub>.

- This coupled with the MOSFET C<sub>GD</sub> causes a parasitic gate voltage on the bottom side device

- The Miller Feedback current is  $C_{GD} \frac{dV_{DS}}{dt}$

- The parasitic gate voltage is given by

$$V_{GPAR} = R_{G\_BOT} C_{GD} \frac{dV_{DS}}{dt} \left( 1 - e^{-\frac{t}{R_{G\_BOT}(C_{GS} + C_{GD})}} \right)$$

20

- Shoot-through current is usually a problem, however in the case, the  $V_{TH}$  sensitivity of Ishoot is used to track  $V_{TH}$ .

- WARWICK THE UNIVERSITY OF WARWICK

- To increase the shoot-through current

- Large bottoms side R<sub>G</sub>.

- Small top side R<sub>G</sub>.

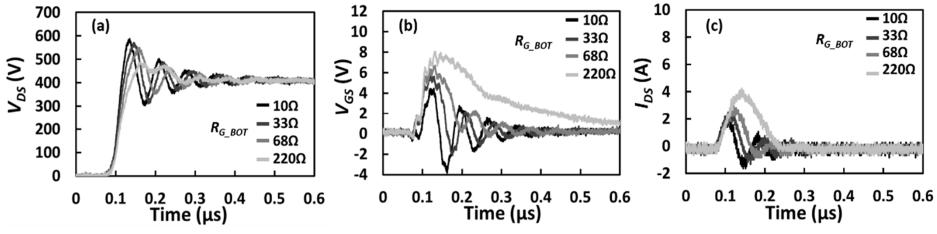

SiC planar MOSFET (a) V<sub>DS</sub> of bottom side device during cross-talk, (b) V<sub>GS</sub> of bottom side device during cross-talk, (c) I<sub>shoot</sub> of bottom side device during cross-talk 21

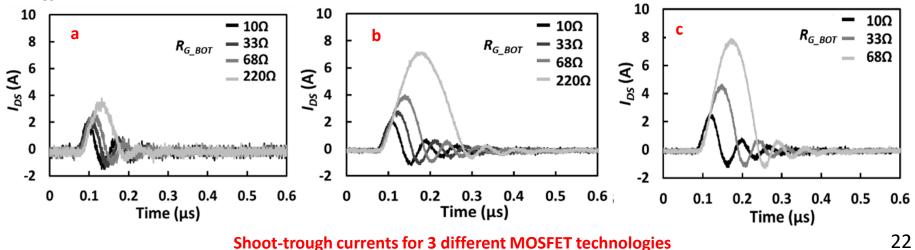

• Different SiC MOSFETs have different susceptibilities to crosstalk according to the ratio below

Three different MOSFET technologies have been measured for crosstalk

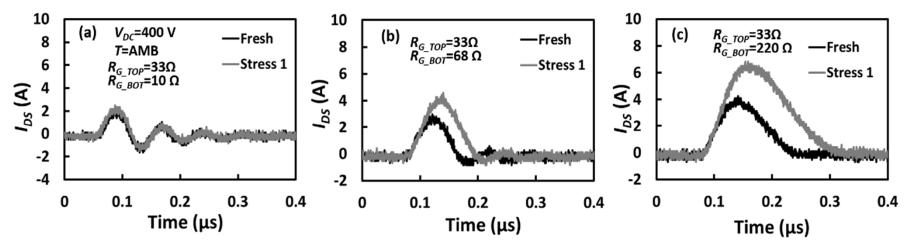

- By choosing the right combination of gate resistances to maximize the shoot-through current,  $V_{TH}$  shift can be monitored.

- The shoot-through increases with NBTI stress (due to decreasing  $V_{TH}$ ) and decreases with PBTI stress (due to increasing  $V_{TH}$ ).

Shoot-through currents for different R<sub>G</sub> combinations on SiC MOSFETs after NBTI stress

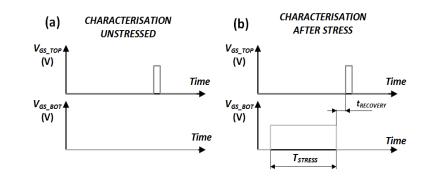

- In the previous measurements, V<sub>TH</sub> recovery was not taken into account.

- By tuning the stress and recovery times, it is possible characterise the BTI stress and recovery mechanisms.

- This technique is an improvement from traditional techniques that simply rely to extracting the static measurements.

Gate driver board

Gate driver boa

$\leq R_{LOAD}$  (V)

**Circuit and Picture Test rig for using crosstalk**

**(Г)**

$V_{DC}$  (\*)

÷

С

UNIVERSITY OF WARWIC

Stress and characterisation sequence

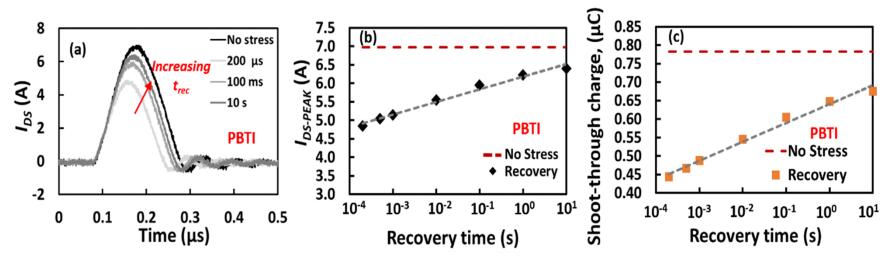

- The measurements below show the  $V_{TH}$  rise with a corresponding reduction in shoot-through current.

- With increasing recovery time, the shoot-through increases back to the unstressed value, thereby indicating a recovery in V<sub>TH</sub>.

Threshold voltage stress and recovery using the proposed technique

- The measurements below show the  $V_{\text{TH}}$  fall with a corresponding increase in shoot-through current.

- With increasing recovery time, the shoot-through reduces back to the unstressed value, thereby indicating a recovery in  $V_{\text{TH}}.$

Threshold voltage stress and recovery using the proposed technique

# **Gate characteristics in GaN HEMTs**

Dr Jose Ortiz Gonzalez 11<sup>th</sup> of January 2021

WARWICK THE UNIVERSITY OF WARWICK

## CONTENTS/OUTLINE

## Introduction

- Gate Characteristics

- Third Quadrant Characteristics

- Gate Stresses and threshold voltage instability

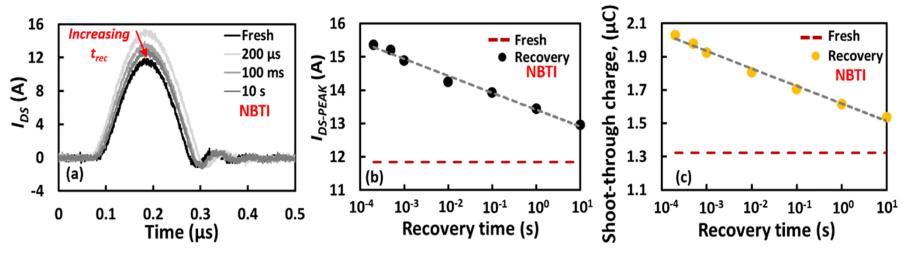

## INTRODUCTION

- GaN devices are well recognized for their ultra-fast switching rates and good conduction losses.

- The good performance of GaN High Electron Mobility Transistors (HEMTs) is due to the two-dimensional electron gas (2DEG) formed at the AlGaN/GaN interface.

- The commercially available devices in the 650 V application range are lateral devices with two main gate structures for achieving normally-OFF operation

[1] T. Detzel, "Reliability of GaN Power Devices from the Industrial Perspective - Tutorial," presented at the 29th European Symposium on Reliability of Electron Devices, Failure Physics and Analysis - ESREF, September, 2018

[2] Y. Uemoto et al., "Gate Injection Transistor (GIT)—A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation," IEEE Trans. on Electron Devices, vol. 54, no. 12, pp. 3393-3399, 2007.

[3] A. N. Tallarico et al., "Investigation of the p-GaN Gate Breakdown in Forward-Biased GaN-Based Power HEMTs," IEEE Electron Device Letters, vol. 38, no. 1, pp. 99-102, 2017.

## INTRODUCTION

- Commercially available GaN HEMTs have been the subject of different studies, including electrothermal characterization and reliability.

- JEDEC committee (JC-70) focused on the development of standards for GaN power devices

- Relevant studies for GaN power devices include:

- Dynamic ON-state resistance

- Threshold voltage instability

- Power Cycling

- Previous studies highlight the **complexity** of the gate stack structure

- Different threshold voltage shifts depending on the magnitude of the gate stress voltage have been reported

## INTRODUCTION

- Two commercially available normally-OFF GaN HEMTs have been studied

- Similar voltage and current ratings

Prototype PCBs for testing DC heater for adjusting the case temperature

## CONTENTS/OUTLINE

- Introduction

- Gate Characteristics

- Third Quadrant Characteristics

- Gate Stresses and threshold voltage instability

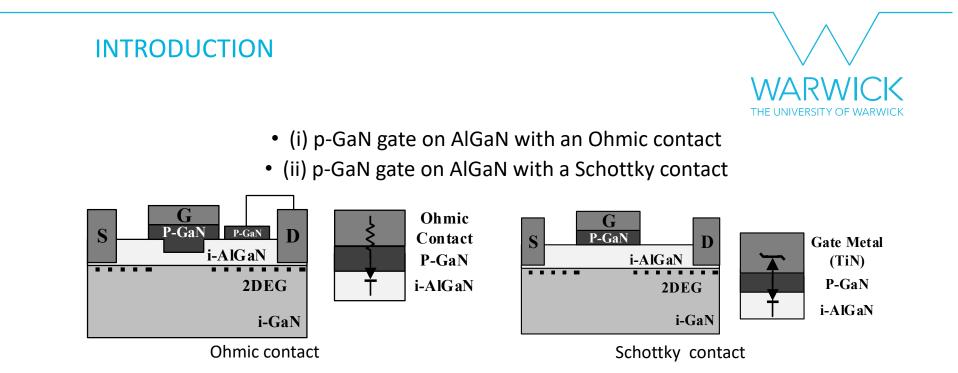

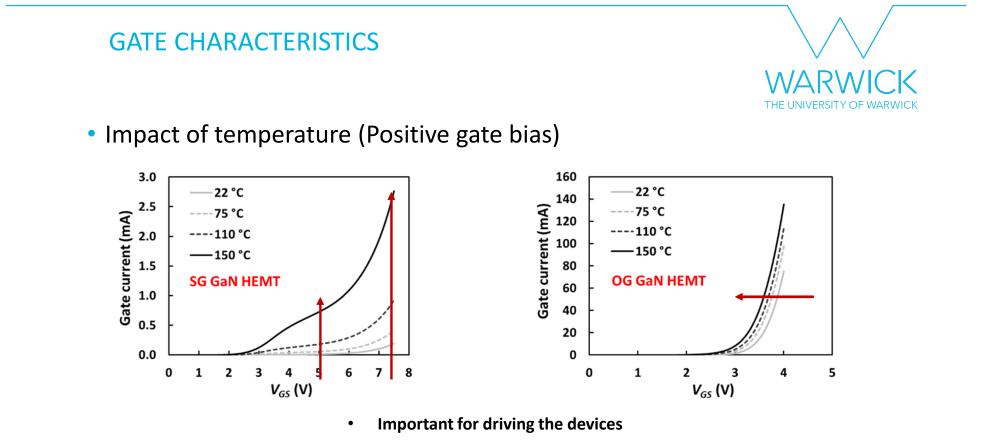

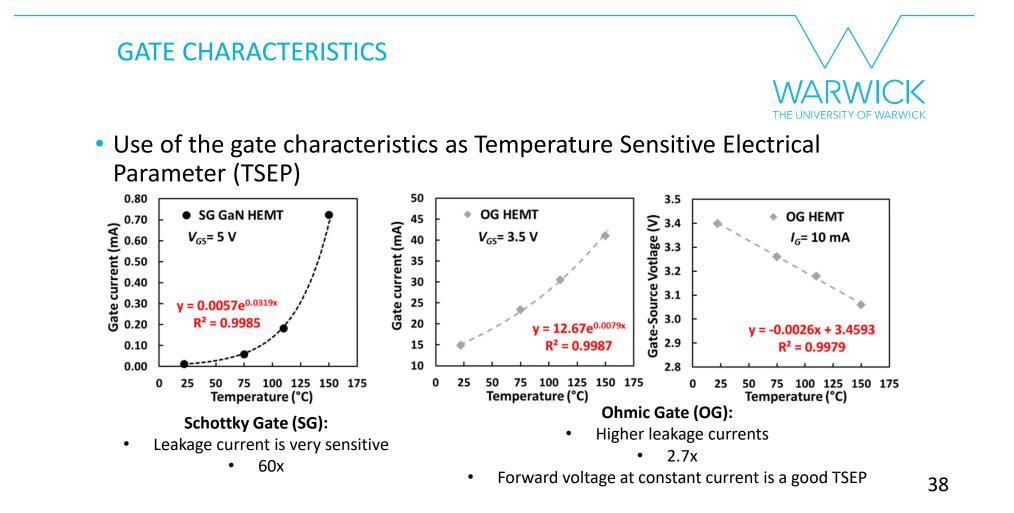

## GATE CHARACTERISTICS

- Different gate structures mean different gate driving requirements.

- Gate reliability is key

- Gate voltage limits

- Gate leakage current

- Role of temperature

#### • Studies are required: Our contribution

J. O. Gonzalez, B. Etoz and O. Alatise, "Characterizing Threshold Voltage Shifts and Recovery in Schottky Gate and Ohmic Gate GaN HEMTs," 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 2020, pp. 217-224,

J. O. Gonzalez, B. Etoz and O. Alatise, "Gate stresses and threshold voltage instability in normally-OFF GaN HEMTs," 2020 22nd European Conference on Power Electronics and Applications (EPE'20 ECCE Europe), Lyon, France, 2020, pp. P.1-P.10,

# CONTENTS/OUTLINE

- Introduction

- Gate Characteristics

- Third Quadrant Characteristics

- Gate Stresses and threshold voltage instability

### THIRD QUADRANT CHARACTERISTICS

- GaN HEMTs do not have a parasitic body diode

- Reverse conduction. What is the mechanism?

- GaN HEMT: Symmetric device

- Reverse Conduction Mechanism:

- Self-commutated reverse conduction (SCRC)

$$V_{SD} = V_{GD-TH} - V_{GS} + I \cdot R_{SD}$$

$$V_{GD-TH} \sim V_{GS-TH}$$

Adapted from: E. A. Jones et al. "Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges," IEEE J. Emerg. Sel. Topics Power Electron., vol. 4, no. 3, pp. 707-719, 2016.

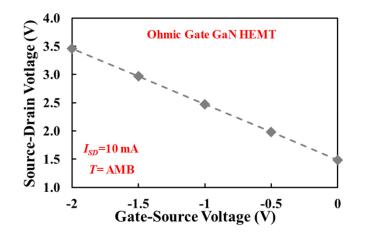

#### THIRD QUADRANT CHARACTERISTICS

- Negative gate voltage

- Gate-Source voltage V<sub>GS</sub> adds to Source-Drain Voltage V<sub>SD</sub>

- Gate and source shorted ( $V_{GS}=0$ )

- Low current /

$$V_{SD} = V_{TH} - V_{GS} + I \cdot R_{SD}$$

$$V_{SD} \sim V_{TH}$$

• Third Quadrant Voltage ( $V_{SD}$ ) at low current and  $V_{GS}$ =0 can be used as an indicator for  $V_{TH}$  tracking

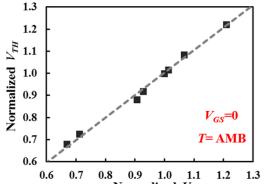

#### THIRD QUADRANT CHARACTERISTICS

- Method for characterizing V<sub>TH</sub> shifts in SiC MOSFETs using the body diode.

- Similar to the use of V<sub>SD</sub> as temperature sensor

- It requires a calibrated relationship between  $V_{SD}$  and  $V_{TH}$

- GaN HEMTs

- There is direct a relationship between  $V_{SD}$  and  $V_{TH}$

|                        | V <sub>TH</sub> (V)<br>V <sub>GS</sub> =V <sub>DS</sub> @ /= 10 mA | V <sub>SD</sub> (V),<br>V <sub>GS</sub> =0, @ / = 10 mA |

|------------------------|--------------------------------------------------------------------|---------------------------------------------------------|

| Ohmic Gate GaN HEMT    | 1.478                                                              | 1.483                                                   |

| Schottky Gate GaN HEMT | 1.597                                                              | 1.576                                                   |

J. A. O. González and O. Alatise, "A Novel Non-Intrusive Technique for BTI Characterization in SiC MOSFETs," in IEEE Transactions on Power Electronics, vol. 34, no. 6, pp. 5737-5747, June 2019,

42

# CONTENTS/OUTLINE

- Introduction

- Gate Characteristics

- Third Quadrant Characteristics

## Gate Stresses and threshold voltage instability

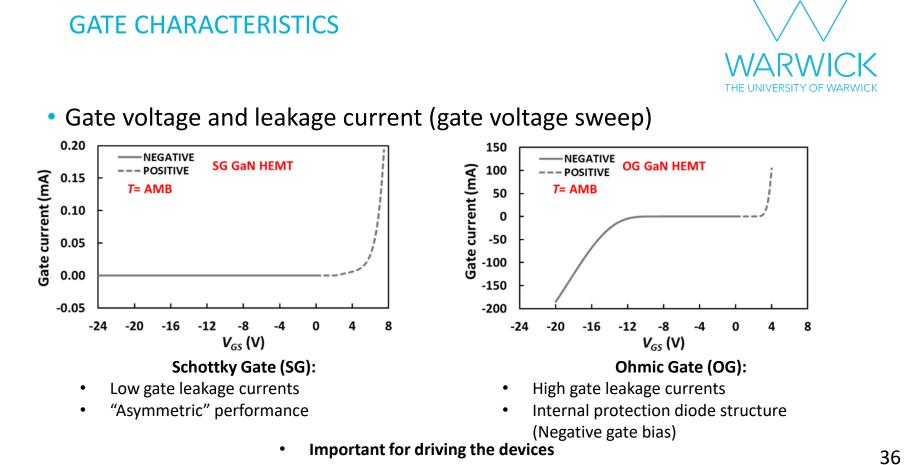

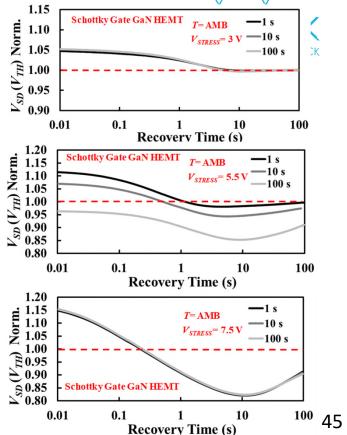

- We evaluated the third quadrant methodology in GaN devices for characterizing  $V_{TH}$  drift after gate stress

- Gate voltage stress for the Schottky gate HEMT

- Gate current stress for the Ohmic gate HEMT

- Different stress parameters can be evaluated:

- Stress time

- Gate stress voltage/current

- Temperature

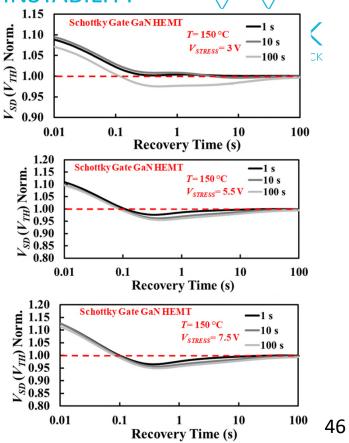

Example for a 3 V/10 s stress pulse

- Schottky Gate HEMT

- Single Pulse stress Ambient temperature

- $V_{TH}$  shift dependent on gate stress level

- The different shifts attributed to three different mechanisms: electron trapping at the AlGaN/GaN interface, hole trapping in the AlGaN barrier and hole depletion

- The different time constants of the traps can be captured using this method

- Stress duration (1 s to 100 s) has no apparent or very minor effect at 3 V and 7.5 V stresses

- Affects peak shift when stress is 5.5 V

- Schottky Gate HEMT

- Single Pulse stress 150 °C

- Compared with ambient temperature, the gate stress level has a minor role on the  $V_{TH}$  shift

- Minor impact of stress time on the V<sub>TH</sub> shift.

More apparent at 3 V gate stress.

- Recovery is accelerated with temperature (range of minutes at ambient temperature)

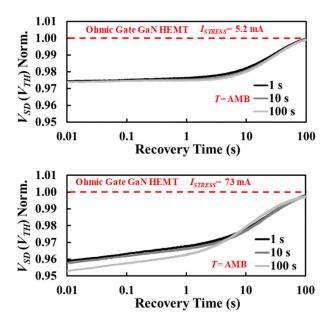

- Ohmic Gate HEMT

- Single Pulse stress Ambient temperature

- Stress in current level: 5.2 mA and 73 mA (Gate voltages of 3.2 and 4 V respectively)

- Negative  $V_{TH}$  shift in both cases. Recovery time in the range of seconds

- $V_{TH}$  shift increases with stress magnitude (-2.5% at low current and -4% at high current)

- Stress time, minor impact at high current stress.

VARWICK

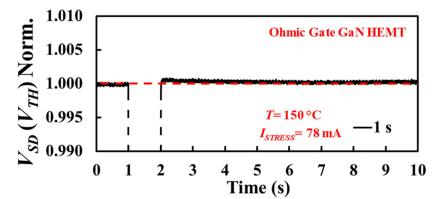

- Ohmic Gate HEMT

- Single Pulse stress 150 °C

- No apparent shift at high temperature stress. Stress current increases (constant voltage gate driver)

# **SUMMARY** • Gate characteristics in WBG devices remain a relevant and important reliability topic

- Different techniques are required for assessing gate characteristics in WBG devices

- We have introduced 2 novel techniques based on 3<sup>rd</sup> quadrant characteristics and cross-talk

- This is especially important when considering TSEPs for condition monitoring of WBG devices

## ACKNOWLEDGEMENTS

- This work was supported by the UK Engineering and Physical Sciences Research Council (EPSRC) through the grant reference EP/R004366/1

- We would like to thank iMAPS UK for the opportunity to disseminate our research

Engineering and Physical Sciences Research Council